DIONEER®

85 - 88 88 - 30 98869338 - 75C

(R)

- For the servicing these models, please refer to the following service manual.

- PD-7050/KU, KC, HEM, HB, SD types and PD-7050-S/HEM type; ARP1331

- PD-6050/KU, KC, HEM, HB, SD, SD/G types and PD-6050-S/HEM type; ARP1329

- PD-5050/HEM, HB types and PD-5050-S/HEM type; ARP1330

- PD-4050/KU, KC, HEM, HB, HP, SD, SD/G types and PD-4050-S/HEM, HB types; ARP1332

# CONTENTS

| 1. IC DATA                     | <br>2  |

|--------------------------------|--------|

| 2. OPTICAL PATH IN THE PICK-UP | <br>8  |

| 3. BLOCK DIAGRAM               | <br>11 |

| 4. CIRCUIT DESCRIPTIONS        | <br>13 |

PIONEER ELECTRONIC CORPORATION 4-1, Meguro 1-Chome, Meguro-ku, Tokyo 153, Japan PIONEER ELECTRONICS SERVICE INC. P.O. Box 1760, Long Beach, California 90801 U.S.A. PIONEER ELECTRONICS OF CANADA, INC. 505 Cochrane Drive, Markham, Ontario L3R 6B8 Canada TEL: [416] 479-4411 PIONEER ELECTRONIC [EUROPE] N.V. Keetberglaan 1, 2740 Beveren, Belgium TEL: 03/775 • 28 • 08 PIONEER ELECTRONICS AUSTRALIA PTY. LTD. 178-184 Boundary Road, Braeside, Victoria 3195, Australia TEL: [03] 580-9911

MT ©MAR. 1987 Printed in Japan

SERVICE GUIDE

60

**ORDER NO.**

ARP1352

# 1. IC DATA

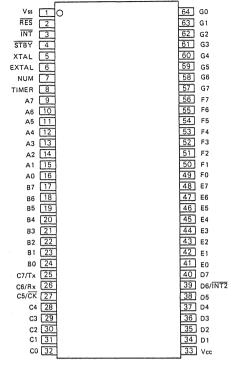

1.1 PD3091A (Only for PD-7050 and PD-7050-S types)

(Top view)

# **Terminal description**

| No | SYMBOL | NAME     | 1/0 | OPERATING DESCRIPT                     | OPERATING DESCRIPTION |  |  |

|----|--------|----------|-----|----------------------------------------|-----------------------|--|--|

| 1  | Vss    |          |     | GND                                    |                       |  |  |

| 2  | RES    | REST     | 1   | CPU RESET input                        | RESET RUN             |  |  |

| 3  | INT    | SCOR     | 1   | SUBCODE SYNC input                     | SYNC                  |  |  |

| 4  | STBY   | emails   | I   | +5V (CPU Standby input)                | STANDBY RUN           |  |  |

| 5  | XTAL   |          |     | Internal Clock Circuit input           | · · ·                 |  |  |

| 6  | EXTAL  |          | _   | Internal Clock Circuit input           | · ·                   |  |  |

| 7  | NÚM    |          | -   | GND (for manufacturer's use)           |                       |  |  |

| 8  | TIMER  | Not used | 1   | (Connected to SEMS)                    |                       |  |  |

| 9  | A7     | TEST     | 1   | TEST Mode Select input                 |                       |  |  |

| 10 | A6     | ALAT     | 0   | Attenuation Level Latch Pulse output   | RUN                   |  |  |

| 11 | A5     | ADAT     | 0   | Attenuation Level data                 | 0 1 2 3 4 5 6 7       |  |  |

| 12 | A4     | ACLK     | 0   | Attenuation Level clock                | ากกกกกก               |  |  |

| 13 | A3     | SRES     | 0   | Key-Display Microcomputer RESET output | It RUN RESET          |  |  |

| 14 | A2     | XLT      | 0   | LSI Control Data RUN Pulse output      | RUN                   |  |  |

| 15 | A1     | Not used | 0   | (OPEN)                                 |                       |  |  |

| 16 | A0     | Not used | 0   | (OPEN)                                 |                       |  |  |

| 17 | B7     | CLMP     | 1   | Disc CLAMPed SW input                  | CLAMP NOT             |  |  |

| 18 | B6     | OPEN     | I   | Disc Tray OPENed SW input              | OPEN NOT              |  |  |

| 19 | B5     | INSD     | 1   | Slider Inside SW input                 | INSIDE                |  |  |

| 20 | B4     | SENS     | 1   | LSI Operating Status Multi-Mode input  |                       |  |  |

| 21 | В3     | CPCF     | 1   | SUBCODE Q-CRC Result input             | NGOK                  |  |  |

| 22 | B2     | GFS      | 1   | FRAME SYNC Lock input                  | NG LOCK               |  |  |

| 23 | B1     | Not used | 1   | Connected to GND                       |                       |  |  |

| No   | SYMBOL | NAME                                   | 1/0 | OPERATING DESCRIP                      | TION                                  |

|------|--------|----------------------------------------|-----|----------------------------------------|---------------------------------------|

| 24   | B0     | FOK                                    | 1   | Focus OK input                         | NGOK                                  |

| 25   | TX(SO) | DATA                                   | 0   | LSI Control Data Serial output         | 0 1 2 3 4 5 6 7                       |

| 26   | RX(SI) | SUBQ                                   | 1   | SUBCODE Q Data input                   |                                       |

| 27   | СК     | CLK                                    | 0   | Serial Transmission clock              | ากกกก                                 |

| 28   | C4     | LDON                                   | 0   | Laser Diode ON/OFF output              | ON OFF                                |

| 29   | C3     | MUTG                                   | 0   | Muting ON/OFF output                   | OFFON                                 |

| 30   | C2     | DEMP                                   | 0   | De-emphasis ON/OFF output              | ON OFF                                |

| 31   | C1     | CLVH                                   | 0   | During Spindle CLV-H = "H"             | CLV-H                                 |

| 32   | C0     | Not used                               | 0   |                                        |                                       |

| 33   | Vcc    | ······································ |     | +5V                                    |                                       |

| 34   | D1     | KD0                                    | 1   | Main Unit Key Code input (LSB)         |                                       |

| 35   | D2     | KD1                                    | 1   | Main Unit Key Code input (LSB)         |                                       |

| 36   | D3     | KD2                                    | 1   | Main Unit Key Code input (LSB)         |                                       |

| 37   | D4     | KD3                                    | 1   | Main Unit Key Code input (LSB)         |                                       |

| 38   | D5     | KD4                                    | 1   | Main Unit Key Code input (MSB)         |                                       |

| 39   | D6     | KS                                     | 1   | Main Unit Key Strobe input             | <u>ON</u> OFF                         |

| 40   | D7     | STS                                    | 1   | Enable Display Data Send input         | DISABLE ENABLE                        |

| 41   | E0     | SCK                                    | 0   | Display Data Serial Transmission Clock | JUUU                                  |

| 42   | E1     | SD                                     | 0   | Display Data Serial output             |                                       |

| 43   | E2     | LIN                                    | 0   | Disk Tray Loading                      | ree & Break IN                        |

| 44   | E3     | LOUT                                   | 0   | IN/OUT output                          | OUT                                   |

| 45   | E4     | Not used                               | 0   | (OPEN)                                 |                                       |

| 46   | E5     | Not used                               | 0   | (OPEN)                                 |                                       |

| 47   | E6     | Not used                               | 0   | (OPEN)                                 |                                       |

| 48   | E7     | Not used                               | 0   | (OPEN)                                 |                                       |

| 49   | FO     | Not used                               | 0   | (OPEN)                                 |                                       |

| 50   | F1     | Not used                               | 0   | (OPEN)                                 |                                       |

| 51   | F2     | Not used                               | 0   | (OPEN)                                 |                                       |

| 52   | F3     | ATTL                                   | 0   | FL: [ATT, -, dB] Segment output        | ONOFF                                 |

| 53   | F4     | IDXL                                   | 0   | FL: [INDEX] Segment output             | ONOFF                                 |

| 54   | F5     | WDWL                                   | 0   | FL: [MUSIC WINDOW] Segment output      | ON OFF                                |

| 55   | F6     | PLYL                                   | 0   | Play LED output                        | OFFON                                 |

| 56   | F7     | PASL                                   | 0   | Pause LED output                       | OFFON                                 |

| 57   | G7     | Not used                               | 1   | Connected to +5V                       |                                       |

| 58   | G6     | RKS                                    | 1   | Remote-Control Key Strobe input        | ON OFF                                |

| 59   | G5     | RKD5                                   | 1   | Remote-Control Key Code input (MSB)    |                                       |

| 60   | G4     | RKD4                                   | 1   | Remote-Control Key Code input (MSB)    |                                       |

| 61   | G3     | RKD3                                   | 1   | Remote-Control Key Code input (MSB)    |                                       |

| 62   | G2     | RKD2                                   | 1   | Remote-Control Key Code input (MSB)    | · · · · · · · · · · · · · · · · · · · |

| 63   | G1     | RKD1                                   | 1   | Remote-Control Key Code input (MSB)    |                                       |

| 1 30 | 1      |                                        |     |                                        |                                       |

З

.

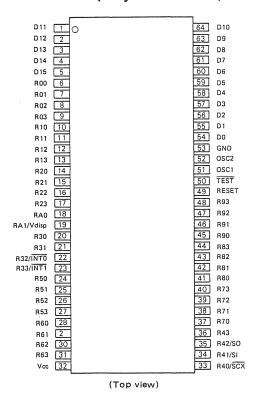

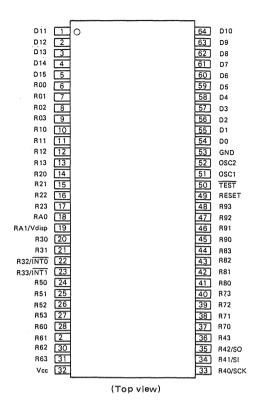

1.2 PD3092A (Only for PD-6050, PD-6050-S, PD-5050 and PD-5050-S types)

# **Terminal description**

| No | SYMBOL | 1/0 | NAME     | DESCRIPTION                                          |

|----|--------|-----|----------|------------------------------------------------------|

| 1  | D11    | 0   | DIG2     | Digital output for FL driving _ON <sup>5V</sup> -26V |

| 2  | D12    | 0   | DIG3     | Digital output for FL driving                        |

| 3  | D13    | 0   | DIG4     | Digital output for FL driving                        |

| 4  | D14    | 0   | DIG5     | Digital output for FL driving                        |

| 5  | D15    | 0   | DIG6     | Digital output for FL driving                        |

| 6  | R00    | 0   | SEG.a    | Segment output for FL driving ON 5V OFF - 26V        |

| 7  | R01    | 0   | SEG.b    | Segment output for FL driving ON OFF                 |

| 8  | R02    | 0   | SEG.c    | Segment output for FL driving ON OFF                 |

| 9  | R03    | 0   | SEG.d    | Segment output for FL driving ON OFF                 |

| 10 | R10    | 0   | SEG.e    | Segment output for FL driving ON OFF                 |

| 11 | R11    | 0   | SEG.f    | Segment output for FL driving ON OFF                 |

| 12 | R12    | 0   | SEG.g    | Segment output for FL driving ON OFF                 |

| 13 | R13    | 0   | SEG.h    | Segment output for FL driving ON OFF                 |

| 14 | R20    | I   | KD0      | Key Scan input Key key _5V _ 26V                     |

| 15 | R21    | Ι   | KD1      | Key Scan input Key                                   |

| 16 | R22    | 1   | KD2      | Key Scan input Key                                   |

| 17 | R23    | ١   | KD3      | Key Scan input Key                                   |

| 18 | RA0    | 1   | Not used | (GND)                                                |

| 19 | Vdisp  | —   |          | Buffer power for FL driving (-26V)                   |

| 20 | R30    | 1   | Not used | (GND)                                                |

| 21 | R31    | 0   | XLT      | LSI Control Data Latch pulse                         |

| 22 | INTO   | 1   | SCOR     | SUBCODE SYNC S0+S1 inputSYNC                         |

| 23 | R33    | 1   | SENS     | LSI Operating Status Multi-Mode input                |

| No | SYMBOL | 1/0 | NAME     | DESCRIPTION                                     |

|----|--------|-----|----------|-------------------------------------------------|

| 24 | R50    | 1   | CRCF     | SUBCODE Q-CRC Result input NG OK                |

| 25 | R51    | 1   | GFS      | Frame Sync Lock input NG LOCK                   |

| 26 | R52    | 1   | Not used | (GND)                                           |

| 27 | R53    | 1   | FOK      | Focus OK input NG OK                            |

| 28 | R60    | 0   | LDON     | Laser Diode ON/OFF output ON OFF                |

| 29 | R61    | 0   | MUTE     | Muting ON/OFF output OFF ON                     |

| 30 | R62    | 0   | DEMP     | De-emphasis ON/OFF output ON OFF                |

| 31 | R63    | 0   | CLVH     | (CLV/H select output) OFF ON                    |

| 32 | VCC    |     |          | +5V                                             |

| 33 | SCK    | 0   | CLK      | Serial clock                                    |

| 34 | SI     | 1   | SUBQ.    | SUBCODE Q Data Serial input 32107654            |

| 35 | SO     | 0   | DATA     | LSI Control Data Serial output 01234567         |

| 36 | R43    | 1   | TEST     | TEST Mode Select input TEST NORMAL              |

| 37 | R70    | 0   | Not used | (NC)                                            |

| 38 | R71    | 0   | Not used | (NC)                                            |

| 39 | R72    | 0   | Not used | (NC)                                            |

| 40 | R73    | 0   | Not used | (NC)                                            |

| 41 | R80    | 0   | Not used | (NC)                                            |

| 42 | R81    | 0   | Not used | (NC)                                            |

| 43 | R82    | 0   | LIN      | Disc Tray Loading IN                            |

| 44 | R83    | 0   | LOUT     | IN/OUT output BRAKE OUT                         |

| 45 | R90    | 1   | OPEN     | Disc Tray OPENed SW input OPEN NOT              |

| 46 | R91    | 1   | CLMP     | Disc CLAMPed SW input CLAMP NOT                 |

| 47 | R92    | Ι   | INSD     | Slider Inside SW input INSIDE NOT               |

| 48 | R93    | Ι   | Not used | (GND)                                           |

| 49 | Reset  | —   |          | CPU Reset input Reset RUN                       |

| 50 | TEST   | -   |          | +5V                                             |

| 51 | OSC1   | I   |          | Clock Circuit input                             |

| 52 | OSC2   | 0   | Not used |                                                 |

| 53 | GND    | —   |          | GND                                             |

| 54 | D0     | 1   | RKS      | Remote-Control Strobe input IN OFF              |

| 55 | D1     | 1   | RKD5     | Remote-Control Code input (MSB)                 |

| 56 | D2     | 1   | RKD4     | Remote-Control Code input (MSB)                 |

| 57 | D3     | 1   | RKD3     | Remote-Control Code input (MSB)                 |

| 58 | D4     | I   | RKD2     | Remote-Control Code input (MSB)                 |

| 59 | D5     | Ι   | RKD1     | Remote-Control Code input (MSB)                 |

| 60 | D6     | 1   | RKD0     | Remote-Control Code input (LSB)                 |

| 61 | D7     | 0   | Not used | (NC)                                            |

| 62 | D8     | 0   | Not used | (NC)                                            |

| 63 | D9     | 0   | DIG0     | Digital output for FL driving $ON^{+5V}_{-26V}$ |

| 64 | D10    | 0   | DIG1     | Digital output for FL drivingON                 |

.

# 1.3 PD3093A (Only for PD-4050 and PD-4050-S types)

**Terminal description**

| -  |        |     |          |                               |           |  |  |

|----|--------|-----|----------|-------------------------------|-----------|--|--|

| No | SYMBOL | 1/0 | NAME     | DESCRIPTION                   |           |  |  |

| 1  | D11    | 0   | REPL     | REPEAT-LED ON/OFF ON O        |           |  |  |

| 2  | D12    | 0   | Not used | (NC)                          |           |  |  |

| 3  | D13    | 0   | PGML     | PROGRAM-LED ON/OFF            | ON OFF    |  |  |

| 4  | D14    | 0   | DIG0     | Digital output                | ON OFF    |  |  |

| 5  | D15    | 0   | DIG1     | Digital output                | ON OFF    |  |  |

| 6  | R00    | 0   | SEG.a    | Segment output for LED        | ON OFF 0V |  |  |

| 7  | R01    | 0   | SEG.b    | Segment output for LED        |           |  |  |

| 8  | R02    | 0   | SEG.c    | Segment output for LED        |           |  |  |

| 9  | R03    | 0   | SEG.d    | Segment output for LED        |           |  |  |

| 10 | R10    | 0   | SEG.e    | Segment output for LED        |           |  |  |

| 11 | R11    | 0   | SEG.f    | Segment output for LED        |           |  |  |

| 12 | R12    | 0   | SEG.g    | Segment output for LED        |           |  |  |

| 13 | R13    | Ι   | KD0      | Key Scan input                | ON OFF    |  |  |

| 14 | R20    | Ι   | KD1      | Key Scan input                | ON OFF    |  |  |

| 15 | R21    | 1   | KD2      | Key Scan input                | ON OFF    |  |  |

| 16 | R22    | 1   | KD3      | Key Scan input                | ON OFF    |  |  |

| 17 | R23    | Ι   | KD4      | Key Scan input                | ON OFF    |  |  |

| 18 | RA0    | 1   | Not used | (GND)                         |           |  |  |

| 19 | Vdisp  |     |          | Buffer power supply GND       |           |  |  |

| 20 | R30    | I   | Not used | (GND)                         |           |  |  |

| 21 | R31    | 0   | XLT      | LSI Control Data Latch pulse  |           |  |  |

| 22 | INTO   | 1   | SCOR     | SUBCODE SYNC S0+S1 input _    | SYNC      |  |  |

| 23 | R33    | 1   | SENS     | LSI Operating Data Multi-Mode | input     |  |  |

6

| No | SYMBOL | 1/0 | NAME                    | DESCRIPTION                                |

|----|--------|-----|-------------------------|--------------------------------------------|

| 24 | R50    | 1   | CRCF                    | SUBCORD Q-CRC Result input NO OK           |

| 25 | R51    | 1   | GFS                     | Frame Sync Lock input NG LOCK              |

| 26 | R52    | 1   | Not used                | (GND)                                      |

| 27 | R53    | Ι   | FOK                     | Focus OK input NG OK                       |

| 28 | R60    | 0   | LDON                    | Laser Diode ON/OFF output ON OFF           |

| 29 | R61    | 0   | MUTE                    | Muting output ON OFF                       |

| 30 | R62    | 0   | DEMP                    | De-emphasis ON/OFF output ON OFF           |

| 31 | R63    | 0   | Not used                | (NC)                                       |

| 32 | VCC    |     |                         | +5V                                        |

| 33 | SCK    | 0   | CLK                     | Serial clock                               |

| 34 | SI     | 1   | SUBQ                    | SUBCODE Q Data Serial input                |

| 35 | SO     | 0   | DATA                    | LSI Control Data Serial output 0 1 2 3 4 5 |

| 36 | R43    | 1   | TEST                    | TEST Mode Select input TEST NORMAL         |

| 37 | R70    | 0   | Not used                | (NC)                                       |

| 38 | R71    | 0   | Not used                | (NC)                                       |

| 39 | R72    | 0   | Not used                | (NC)                                       |

| 40 | R73    | 0   | Not used                | (NC)                                       |

| 41 | R80    | 0   | Not used                | (NC)                                       |

| 42 | R81    | 0   | Not used                | (NC)                                       |

| 43 | R82    | 0   | LIN                     | Disc Tray Loading IN                       |

| 44 | R83    | 0   | LOUT                    | IN/OUT output BRAKE OUT                    |

| 45 | R90    | 1   | OPEN                    | Disc Tray OPENed SW input OPEN NOT         |

| 46 | R91    | 1   | CLMP                    | Disc CLAMPed SW input CLAMP NOT            |

| 47 | R92    | 1   | INSD                    | Slider Inside SW input INSIDE NOT          |

| 48 | R93    | 1   | Not used                | (GND)                                      |

| 49 | Reset  |     |                         | CPU Reset input Reset RUN                  |

| 50 | TEST   | -   |                         | +5V                                        |

| 51 | OSC1   | 1   |                         | Clock Circuit input                        |

| 52 | OSC2   | 0   |                         | (Internal Clock Circuit output)            |

| 53 | GND    | -   | framenan por frankrazy, | GND                                        |

| 54 | D0     | 1   | RKS                     | Remote-Control Key Strobe input IN OFF     |

| 55 | D1     | 1   | RKD5                    | Remote-Control Key Code input (MSB)        |

| 56 | D2     | 1   | RKD4                    | Remote-Control Key Code input (MSB)        |

| 57 | D3     | 1   | RKD3                    | Remote-Control Key Code input (MSB)        |

| 58 | D4     | 1   | RKD2                    | Remote-Control Key Code input (MSB)        |

| 59 | D5     | 1   | RKD1                    | Remote-Control Key Code input (MSB)        |

| 60 | D6     | 1   | RKD0                    | Remote-Control Key Code input (LSB)        |

| 61 | D7     | 0   | Not used                | (NC)                                       |

| 62 | D8     | 0   | Not used                | (NC)                                       |

| 63 | D9     | 0   | PLYL                    | DLAY-LED ON/OFF ON 5V OV                   |

| 64 | D10    | 0   | PASL                    | PAUSE-LED ON/OFF ON 5V OV                  |

7

# 2. OPTICAL PATH IN THE PICK-UP

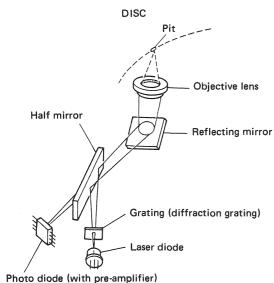

2-1 OPTICAL PATH AND OPTICAL PARTS

# Fig. 2-1 shows the configuration of this pick-up's optical part.

The wavelength of the light emitted from the laser diode is between 780 and 790 nm. The light is barely visible. This light source is spread into an ellipse from an ultra-small emission point. The light expands at a set angle.

The emitted light goes through a grating and is divided into three beams of 0 step and  $\pm 1$  step.

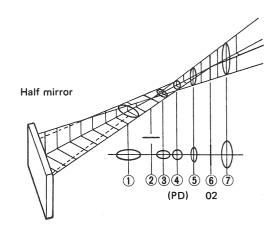

The other beams of  $\pm 2$ , 3, and n steps are also present, but are lost and not used. When the light reaches the half mirror, 50% is reflected. The remaining light permeates the half mirror and is lost.

The light then goes to the reflecting mirror where all the light is reflected to the objective lens (finite type).

Since this pick-up's objective lens uses a finite system (finite because the LD's convergence distance is finite), a collimator lens is unnecessary. The old models objective lenses are called infinite type. The light that is converged on an ultra-small diameter spot by these objective lenses is reflected by the disc and returns to the objective lens. Then it goes through the half mirror where 50% of it returns to the laser diode. The remaining 50% of light goes through and reaches the photo diode.

This has been a general outline of the optical path. The features of each part are explained in the following section.

2-2 FEATURE OF EACH PART

# (1) Laser diode (LD)

The size of previously-used LDs was  $9\phi$ . However, a newlydeveloped LD with a size of  $5.6\phi$  has been introduced. This has resulted in a compact and lightweight optical path.

#### (2) Objective lens

The collimator lens has been replaced by the finite objective lens which has a finite convergence distance for the LD's optical path. This has resulted in lower costs while preserving high performance.

The finite objective lens, like the conventional infinite lens, is a high-performance lens designed to attain sufficient optical performance even when the optical parts are not parallel within the optical path.

#### (3) Half mirror

The light that returns to the objective lens goes through the half mirror. Since the half mirror is a glass plate, it is known that astigmatism is created for the light which enters at an angle. The old model similarly used a glass plate and had a device in its optical part to cancel this astigmatism. Whereas, this new pick-up uses the astigmatism advantageously for the focus servo.

Consequently, the multi-lens used in previous models has not been incorporated in this new pick-up. This has resulted in lower costs while preserving high performance. At the same time, the points of parts have been reduced, improving dispersion and reliablity.

#### (4) Axle-sliding actuator

The position accuracy of the objective lens is an important factor for the optical pick-up. The pick-up has a sliding axle for the actuator which drives the objective lens. Accurate and stable positioning of the objective lens is thus attained, resulting in stable trackability. Also, a smooth frequency response with low resonance is also realized as with the conventional spring-supported type.

#### (5) Resin body

The CD body has been made with computer-simulated technology. To keep body changes to a minimum, resin has been incorporated. Due to the mounting, materials were carefully selected and the same reliability as the previously-used aluminum has been realized.

The use of resin has made possible mounting configurations that were not possible with aluminum. Therefore the use of adhesives has been greatly reduced for improved reliability.

#### 2-3 RF and servo signal

#### (2) RF and servo signals

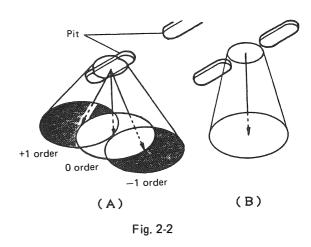

The beam, which has been reduced to an extremely small spot by the objective lens, now strikes the disc side on which the signal is located. Part of the beam is then reflected back to the objective lens and photo diode. A diagram showing how this beam is reflected off the disc is shown in figure 2-2. (A) shows what happens when the concentrated beam is directed at a pit. Normally, this reflected light would disrupt the output light beam. In the laser diodes used in CD players, however, noise is reduced instead, resulting in stable performance. This property is very advantageous for the half prism which allows only half of the light energy to pass.

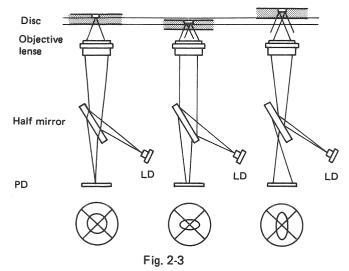

A pit and (B) shows the same beam when reflected from a space between pits. In case (A), the beam is diffracted, so the dark part of the beam does not return to the objective lens. Instead, only the center of the beam passes through the objective lens and reaches the photo diode. In case (B), there is no diffraction because the beam does not strike a pit. Therefore, the entire beam is reflected back to the photo diode, producing brighter beam than when a pit is reached. In this system, the data on the disc, which is represented by pits, is covered into an electrical signal at the photo diode according to the intensity (brightness) of the reflected beam. The RF signal is then produced from this electrical signal by the computation circuit. Fig. 2-3 shows how the focus signal is detected. (1) is when the beam from the laser diode is accurately focused on the disc by the objective lens. (2)shows what happens when the disc comes closer to the pickup and (3) shows what happens when the disc moves farther away. The grating and concave lens, which have no direct effect on the focusing are not shown in the diagram.

In case (1), the beam emanating from point 01 is reflected and diffracted on the disc surface to produce the condensed beam (02). In case (2), the beam is directed at a point farther than that of beam 02. Fig. 2-4 shows the properties of the half mirror. 1 through 7 shows the shape of the beam at each point. Between points 2 and 6, which are in a straight line, the beam is circular at point 4. Point 6 corresponds to beam 02 of fig. 2-3. If we assume that fig. 2-4 shows mode (1) of fig. 2-3, that means the beam is circular because the photo diode is located at point 4. In mode (2) of fig. 2-3, the location of the photo diode is closer to the cylindrical lens than it was in fig. 2-4. That means the shape of the beam is the same as that of point 3 (an ellipse that has a longer width than height). In mode (3) of fig. 2-3, the shape of the beam is that of point 5, an ellipse that has a longer height than width.

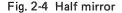

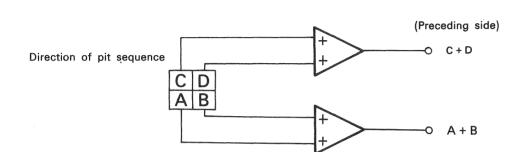

These beam shapes are shown in fig. 2-3. By performing a (A + C) - (B + D) computation using the A-D photo diode quartering elements, the focus signal is produced.

Let's consider what happens as the objective lens is gradually moved closer to the disc. If the objective is fairly far from the disc, only a small amount of light will be returned to the photo diode. Furthermore, since the returning light is quartered, the focus signal would be 0.

If the objective lens is moved closer to the disc until point 7 of fig. 2-4 is reached, the shape of the beam at the photo diode becomes an ellipse that is higher than it is wide.

The focus signal would then be positive because (A + C) is greater than (B + D). However, after the peak (vertical line) is reached at point 6, it begins to return to zero. If it becomes zero at point 4, the beam becomes an ellipse that is wider than it is high because (A + C) is less than (B + D) and the focus signal becomes negative. After peaking at point 2, the focus signal returns to zero just as when the objective lens is too far from the disc. Focusing signals produced in the above manner are shown in fig. 2-5. Due to its shape, this is called an S-curve, an important graph that expresses the properties of the focus signal.

Since the real purpose of the focus servo is to maintain the focus signal at zero, only a tiny section at the center of the S-curve appears as residual error.

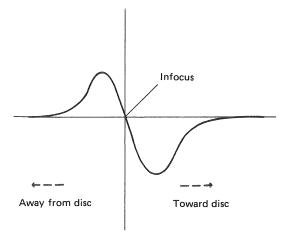

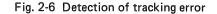

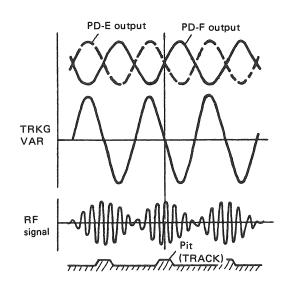

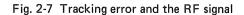

Fig. 2-6 shows how the tracking signal is detected. The beam from the laser diode is divided into three beams. The  $\pm 1$  order beams on either side of the 0 order beam are used to produce the tracking signal. These two beams are, like the 0 order beam, are directed at the disc in a tiny spot. In principle, the spots of the two side beams are an equal distance from the center spot as shown in fig. 2-6. (The actual distance is much greater than that shown in the figure.) These two side beams are reflected and diffracted and returned to their respective detection elements in the photo diode. If these two elements detect the same intensity from both beams, it can be assumed that the primary (0 order) beam is correctly following the line of pits on the disc. Fig. 2-7 shows the relationship between the track and the output of each photo diode element (A, B and C).

1

# 4. CIRCUIT DESCRIPTIONS

# 4.1 ACCURATE FOCUS SERVO SYSTEM

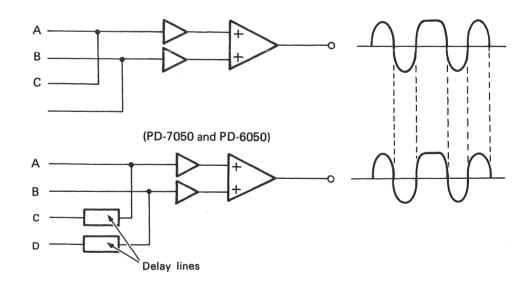

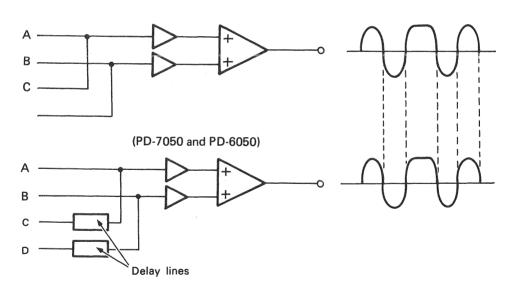

As a method (the Accurate Focus System) for reducing the distortion of RF signals read by the pickup, delays have been applied to the output of 2 photodiodes that precede the quarter photodiodes and is followed by an addition operation in order to achieve improvements in frequency responce, distortion, S/N, and so on as well as to increase the accuracy of signal reading.

(Former Method)

Fig. 4-1

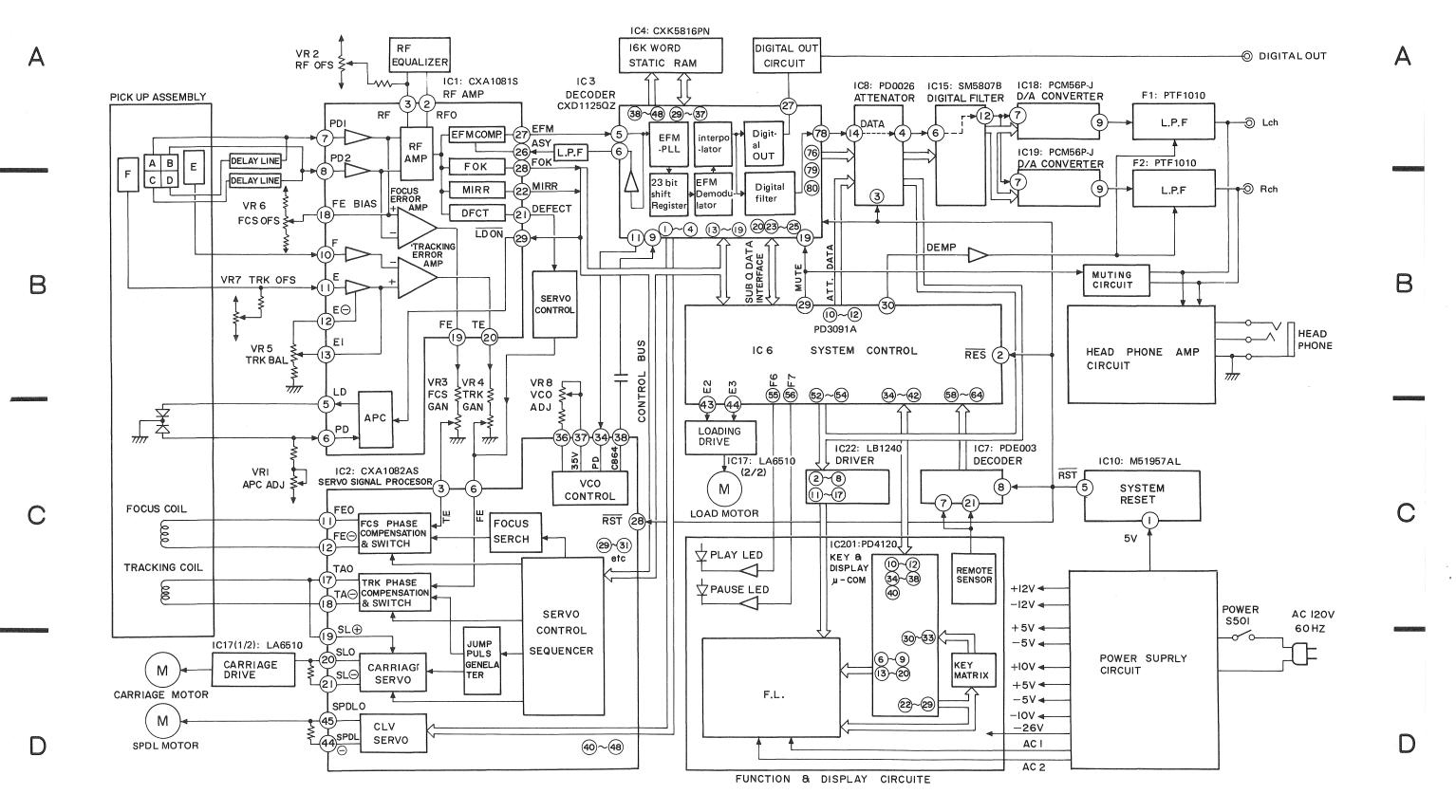

3. BLOCK DIAGRAM

• For PD-7050

З

# PD-7050, PD-6050 PD-5050, PD-4050

# 4. CIRCUIT DESCRIPTIONS

# 4.1 ACCURATE FOCUS SERVO SYSTEM

As a method (the Accurate Focus System) for reducing the distortion of RF signals read by the pickup, delays have been applied to the output of 2 photodiodes that precede the quarter photodiodes and is followed by an addition operation in order to achieve improvements in frequency responce, distortion, S/N, and so on as well as to increase the accuracy of signal reading.

FE >--

0.0

T S

V tl

o a T

c n

Τ

is c

m T

m

ir

14

4

Lanoan and

Fig. 4-1

# 4.2 IC DESCRIPTIONS

#### 4.2.1 CXA1082AS

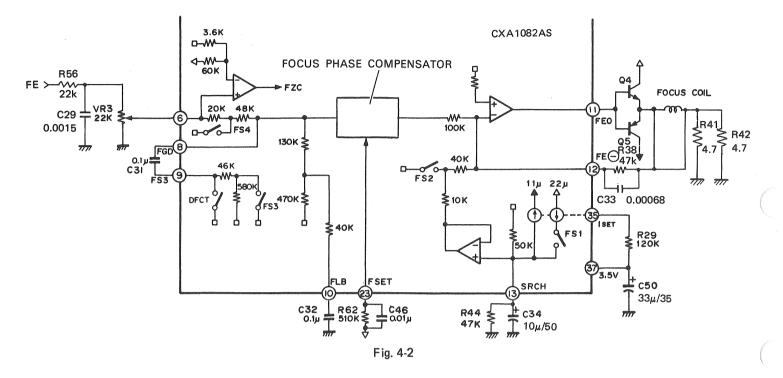

# FOCUS SERVO SYSTEM

The above figure is a block diagram of the Focus Servo System (Fig. 4-2).

When FS3 is ON, the high-cut filter gain that formed the low-range time constant can be dropped by the operation of the capacitor connected between Pins 8 and 9 as well as the internal resistor.

The capacitor between Pin 10 and GND is a time constant that boost the low-range frequency during normal play mode.

The peak frequency of the Focus Phase Compensator is in inverse proportion to the value of the resistor connected to Pin 23, and its peak value is approximately 1.2 kHz in case of  $510k\Omega$  resistance value.

The height of the focus search operation is approximately  $\pm 1.1$  Vp-p in case of the time constants shown in the Fig. 4-2. This height is in inverse proportion to

the value of the resistor connected between Pins 35 and 36.

This system is set to a value that is 5.7% of difference between the reference voltage Vcc for the inverted input of the FZC comparator and VC (Pin 1); that is, it is set to (Vcc - VC)  $\times$  5.7%.

#### NOTE:

When the value of the resistor connected to Pin 23 is changed, changes will also concurrently occur in the peak values of the phase-compensating peak value Focus Servo and Tracking and Carriage Servo systems as well as in the fc value of CVL LPF. In addition, the dynamic range and offset voltage of the OP Amp will also be concurrently changed.

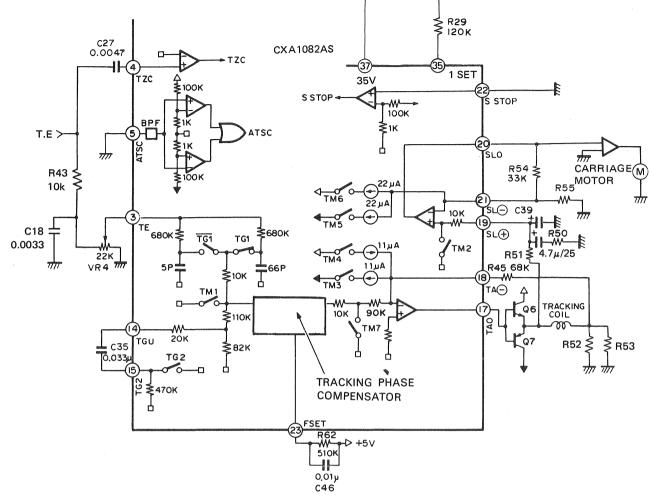

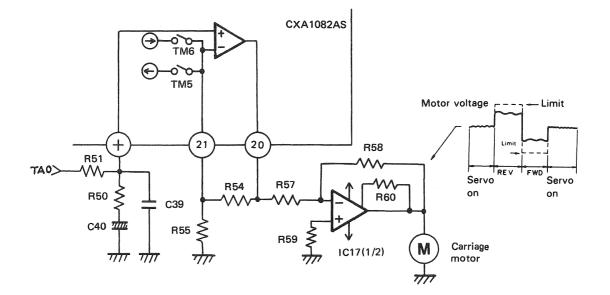

#### TRACKING AND CARRIAGE SERVO SYSTEM

The above figure is a block diagram of the Tracking and Carriage Servo System (Fig. 4-3).

The capacitor connected between Pins 14 and 15 is a time constant that functions to drop the high-range gain when TG2 is OFF. The peak frequency of the Tracking Phase Compensator is also in reverse proportion to the value of the resistor connected to Pin 23, and its peak value is approximately 1.2 kHz in case of  $510k\Omega$  resistance value.

TM3 or TM4 is switched ON in order to make a tracking jump in the FWD (forward) or REV (reverse) direction, respectively. The peak voltage to be applied to the tracking coil at this time is determined by the current value of TM3 or TM4 and the feedback resistor from Pin 18; that is:

Track Jump Peak Voltage =

TM3 (TM4) current value  $\times$  feedback resistance value  $\times \frac{\text{TRK coil DCR}}{\text{R52}//\text{R53}}$  A FWD or REV carriage kick is performed by switching TM5 or TM6 to ON, respectively. The peak voltage to be applied to the carriage motor at this time is determined by the current value of TM5 or TM6 and the feedback resistor from Pin 21; that is:

Carriage Jump Peak Voltage =

TM5 (TM6) current value  $\times$  feedback resistance value  $\times \frac{R58}{R57}$

The current value at each SW is determined by the value of the resistor connected to Pins 35 and 36. When its resistance value is  $120k\Omega$ , the respective current values will be as follows:

TM3, TM4 =  $\pm 11 \ \mu$ A TM5, TM6 =  $\pm 22 \ \mu$ A

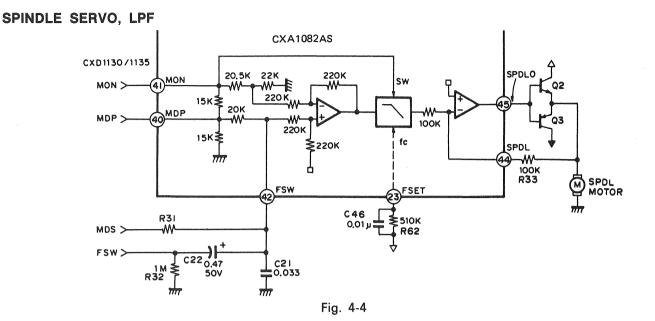

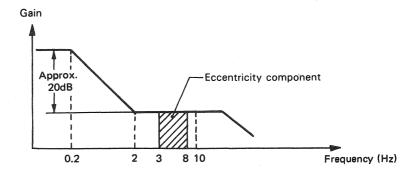

A 200Hz LPF is formed at the 0.033  $\mu$ F connected to Pin 42 and 20k $\Omega$  resistor and a secondary LPF is formed at the built-in LPF (Pin 23: fc - 200 Hz with a 510k $\Omega$  resistor), thereby eliminating the carrier components of the CLV Servo Error signals: MDS and MDP.

In CLV-S Mode, FSW goes low and the fc value of the Pin 42 LPF is lowered to further reinforce the filter.

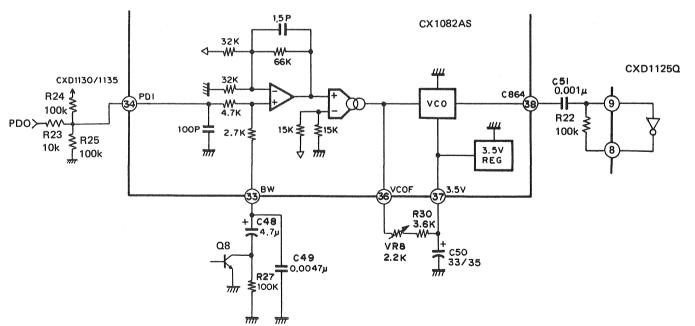

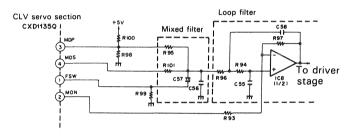

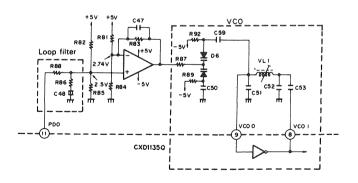

# VCO LOOP FILTER, 8.64MHz VCO

Fig. 4-5

The phase comparison output PDO which is input from Pin 34 subjected to V-I conversion after having its PWM carrier component eliminated at the Loop Filter. It is then added to the current from Pin 36 which is used for setting the free-run frequency in order to control the VCO frequency. The free-run frequency of the VCO is approximately in inverse proportion to the value of the resistor between Pins 36 and 37.

#### COMMAND

The input data used for operating this IC actually consists of eight bits. In the following description, however, each command will be expressed using a two-digit hexadecimal format of \$XX (with X ranging from 0 to F).

- \$0X ( 2 SENS = "FZC") This command is related to the control of the focus servo. Its bit configuration is as follows: D7 D6 D5 D4 D3 D2 D1 D0 0 0 0 FS4 FS3 FS2 FS1 The four focus-related SWs are FS1 to FS4, which respectively correspond to D0 to D3 above.

- \$00 When FS1=0, Pin 13 is charged to:  $(22 \ \mu A 11 \ \mu A) \ \times 50 \ k\Omega = 0.55V$ . Moreover, if FS2=0, this voltage is transmitted no further and the (1) output becomes 0 V.

- \$02 In the above status, only FS2 becomes 1. At this time, a negative output is sent from Pin 11. This voltage level is stipulated as follows:

(22  $\mu$ A - 11  $\mu$ A)  $\times$  50 k $\Omega$   $\times$  Resistance value between (1), (2)/50 k $\Omega$  .....Equation (1)

\$03 In the above status, FS1=1 so that the +22  $\mu$ A power supply is cut off. Next, the Charge/Recharge circuit of CR is formed, and the voltage of Pin 13 drops with time as shown in Fig. 4-6 below.

Fig. 4-6. Pin 13 Voltage when FS1 Changes from 0 to 1

This time constant is stipulated by C34 that is externally connected to  $50k\Omega$ .

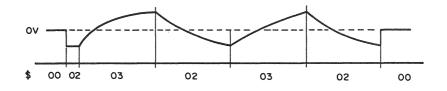

The alternate issuing of 02 and 03 enables the creation of the search voltage for focus. (See Fig. 4-7)

Fig. 4-7. Search Voltage Creation by \$02 and \$03 (Pin 11 Voltage)

# 1-1.Description of FS4

This switch is situated between Focus Error input 6 and the Focus Phase Compensator to receive the Focus Servo ON/OFF data.

$00 \rightarrow 08$ Focus OFF  $\leftarrow$  Focus ON

# 1-2.Procedure for Applying Focus

The following explanation will presume the below polarities:

- (a) The lens is searching the disc in the far-toclose direction.

- (b) At this time, the output voltage (1) changes from negative to positive.

- (c) Furthermore, the S-curve of the focus at this time changes according to Fig. 4-8 below.

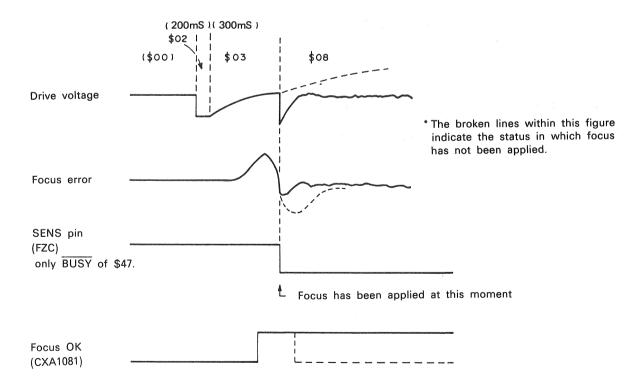

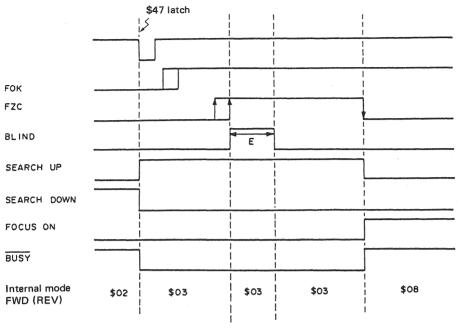

The Focus Servo is applied with Point (A) of Fig. 4-8 as its operating point. The Focus Search operation is performed and the Focus Servo SW is set to ON while Point (A) of Fig. 4-8 is being crossed. In order to also prevent malfunction, the logical product of the operation and the Focus OK signal is obtained.

This IC is designed so that FZC (Focus Zero Cross) will be output - as the signal which indicates the crossing of Point (A) - from the (2) SENS pin. In addition, the Focus OK signal is output as an indication that focus is being applied (or can be applied in this case).

To summarize the above, the focus will be optimally applied in accordance with the time chart below. (In actuality, this IC's auto sequence is being used so the system  $\mu$ -COM only sends \$47 from point(**B**). See auto sequence on page 20.)

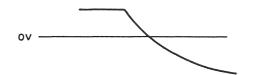

Fig. 4-8 S-Curve of the Focus

Fig. 4-9. Timing Chart of the Focus ON Operation

# 1-3.The 24 SENS Pin

The data which is output by the SENS pin will vary according to the input data as follows. Since FOCS IN and TRACK JUMP are actually done by auto sequencing, the output of CXA1082AS, which uses system  $\mu$ -COM, is only BUSY of \$4X. (See auto sequence on page 20.)

|               | <b>N</b>      | ·····      |

|---------------|---------------|------------|

| \$0X input    | $\rightarrow$ | FZC output |

| \$1X input    | $\rightarrow$ | AS         |

| \$2X input    | $\rightarrow$ | TZC        |

| \$3X input    | $\rightarrow$ | SSTOP      |

| \$4X input    | $\rightarrow$ | BUSY       |

| \$5X-\$7X inj | put →         | HIGH-Z     |

|               |               |            |

Since any data above \$7X is a command code of CXD1135, its connection with the "SENS" pin of CXD1135 will permit the output of various types from a single pin.

# 2. 1X ( 24 SENS = "AS")

This command is related to the ON/OFF status of TG1, TG2 and the Break circuit. Its bit

configuration is as follows: D7 D6 D5 D4 D3 D2 D1 D0 0 0 0 1 ANTI Break TG2 TG1 SHOCK circuit ON/OFF ON/OFF

Brake circuit description

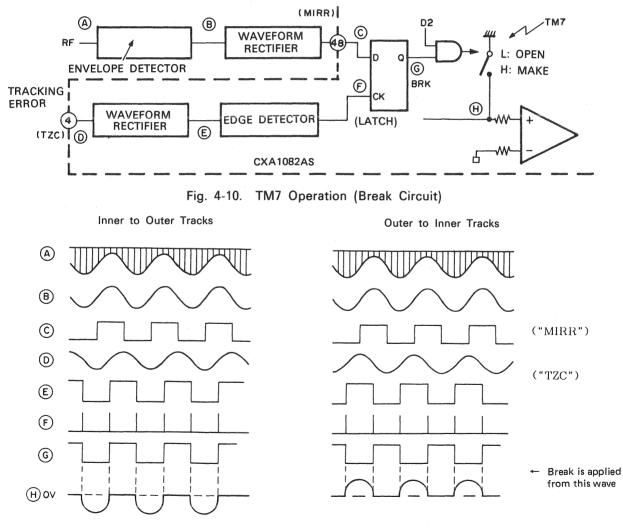

These switches are used to switch the Up/Normal status of the Tracking Servo gain. Because the Servo circuit exceeds the linear range after performing a 100- or 10-track jump, the settling of the actuator becomes extremely bad such that it will, for example, return after jumping only ten tracks, although a 100-track jump was intended, and such phenomena will frequently occur. It is the Break circuit, however, that functions prevent such occurrences. By exploiting the 180° phase offset between the RF envelope and the tracking error due to the direction of the actuator transversing the tracks along the radius from the inner to outer tracks and its reverse direction, the Break circuit cuts out the unnecessary portion of the tracking error and applies a break.

Fig. 4-11. External Waveforms

# 3. Track Jump

This CD player is doing track jumps of 1, 10, 50, 100 via the auto sequence of CXA1082AS. The auto sequence sends the timing data from the system  $\mu$ -COM to the RAM of CXA1082AS beforehand. Therefore just by sending the serial data of the auto sequence, the TRACK JUMP and FOCS are drawn in.

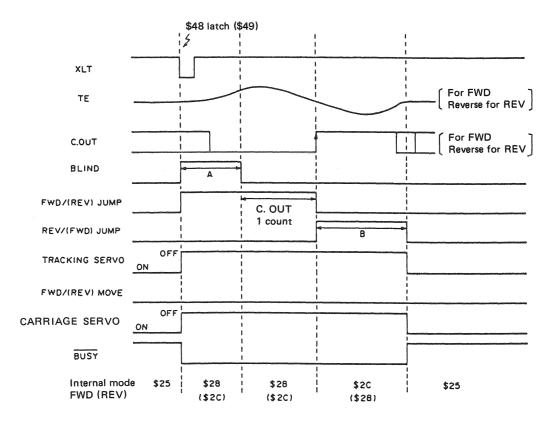

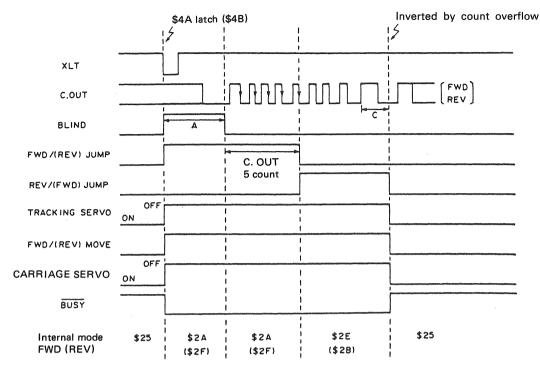

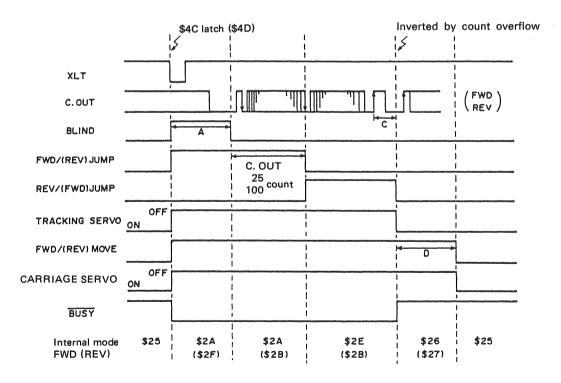

Figures a. to d. show the timing charts of the 1, 10, 50, or 100 track jump and auto sequence.

The time control in the figures is done by setting \$5X with the system  $\mu$ -COM.

Auto sequence starts by the sending of 4X in the table below.

|                      | D3 | D2 | D1 | D0 |

|----------------------|----|----|----|----|

| CANCEL               | 0  | 0  | 0  | 0  |

| FOCUS ON             | 0  | 1  | 1  | 1  |

| 1 TRACK JAMP         | 1  | 0  | 0  | Х  |

| 10 TRACK JAMP        | 1  | 0  | 1  | Х  |

| 100 or 50 TRACK JAMP | 1  | 1  | 0  | X  |

X = 0 FOWARD X = 1 REVERSE

# Auto Sequence Time Chart

#### a. 1 track jump

#### b. 10 track jump

c. 50 track jump

100

21

#### d. Auto focus

Note: This time chart's horizontal axis is not limited to being proportional to real time.

#### 4.2.2 CXA1081S

#### **RF AMP**

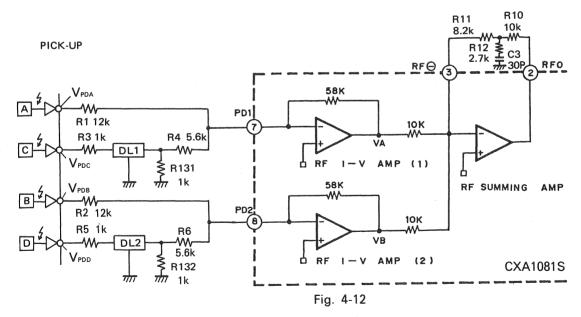

The output voltage of the photodiode that are input to the input pins (PD1 and PD2) are respectively subjected to an increase in voltage of about 5 times into a  $58k\Omega$  equivalent resistor at the RF I-V Amps (1) and (2). Furthermore, addition is performed at the RF Summing Amp so that the output voltage which has been converted from the currents of the photodiodes (A + B + C + D) is output from Terminal RFO. An eye pattern check can be performed at Terminal RFO.

The low-frequency component of the RFO output voltage  $V_{RFO}$  is as follows:

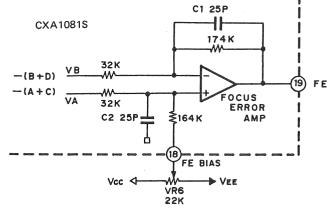

# FOCUS ERROR AMP

This amp obtains the difference between the output (VA) of the RF I-V Amp (1) and the output (VB) of the RF I-V Amp (2), then outputs the voltage which has been converted from the currents of the photodiodes (A + C - B - D).

The FE output voltage (low frequency) is as follows:

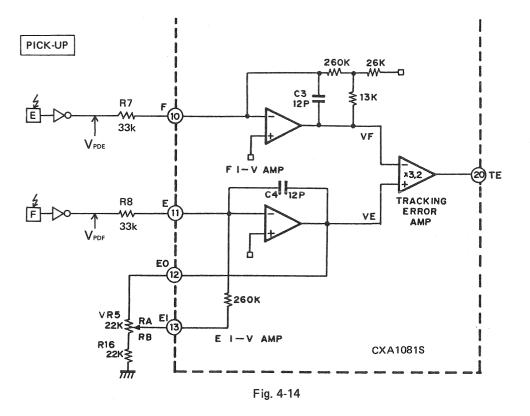

# TRACKING ERROR AMP

The voltage of photodiodes for the side spots input to Terminals E and F are respectively subjected to the voltage is increased at the E I-V and F I-V Amps. That is:

$$VF = \frac{403k\Omega}{33k\Omega} \times V_{PDF}$$

$$VE = [260 \ k\Omega \ X \ RA/(RB + 22k\Omega) + (RA + 260k\Omega)]/33k\Omega \ X \ V_{PDE}$$

Furthermore, the output difference between the E I-V and F I-V Amps is obtained at the Tracking Error Amp in order to obtain the output voltage that has been converted from currents of the photodiodes (E - F) as follows:  $VTE = (VE - VE) \times 3.2$

$$E = (VE - VF) \times 3.2$$

= (V<sub>PDE</sub> - V<sub>PDF</sub>) ×  $\frac{403k\Omega}{33k\Omega}$  × 3.2

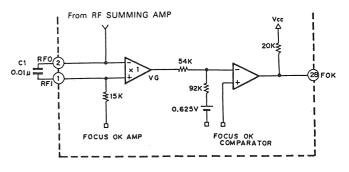

### FOCUS OK CIRCUIT

The Focus OK circuit functions to create the window for the timing of switching ON the Focus Servo from the Focus Search status.

With respect to the RF signal of Pin (2), both its HPF signal and the reciprocal of the LPF output (inverted phase) from the Focus OK Amp output are obtained at Pin (1).

The Focus OK output is inverted in the case below:  $V_{\text{RF1}}$  –  $V_{\text{RF0}}$   $\doteqdot$  -0.39 V

CXA1081S

Fig. 4-15

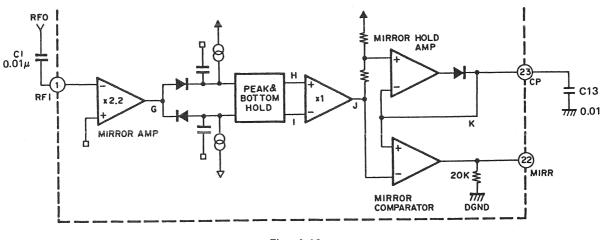

# **MIRROR CIRCUIT**

Fig. 4-16

After amplifying the RFI signal, the Mirror circuit performs Peak Hold and Bottom Hold.

Peak Hold will hold the peak value at a time constant that is capable of tracking even a 30 kHz Traverse signal, whereas Bottom Hold will hold the bottom value at a time constant that is capable of tracking even the envelope fluctuations of revolving cycles.

The DC-replayed Envelope signal J is obtained from the differential amplitude of these Peak and Bottom Hold signals, H and I. The Mirror output is obtained by comparing this signal J with the signal K which has been held at peak level, using a time constant of a a level that is two-thirds that of the peak value. In other words, the Mirror output is "L" upon a disc track or "H" between disc tracks (the Mirror section). Moreover, the Mirror output is also "H" when a defect has been detected.

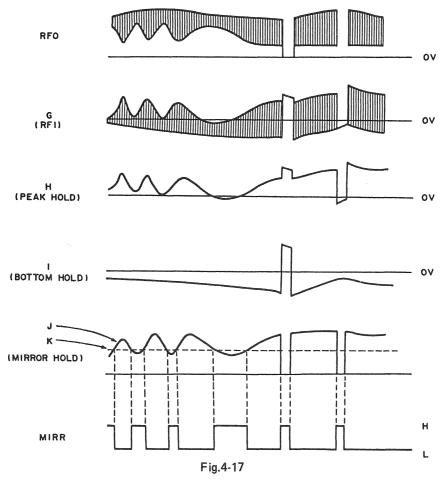

# EFM COMPARATOR

The EFM Comparator functions to convert the RF signals into binary signals. The asymmetry caused by variance during disc manufacture cannot be eliminated merely by AC coupling. Consequently,

the reference voltage of the EFM comparator is controlled by exploiting the respective 50% probability of a 1 or 0 occurring as the value of a binary-coded EFM signal.

### PD-7050, PD-6050 PD-5050, PD-40<u>50</u>

Note that since this EFM Comparator is of power-current SW type, its H and L levels will not equal the supply voltage, there is feedback via the decoder's C-MOS Buffer.

R20, R21, C16, and C17 serve as a LPF for obtaining the DC of (Vcc + DGND)/2 [V].

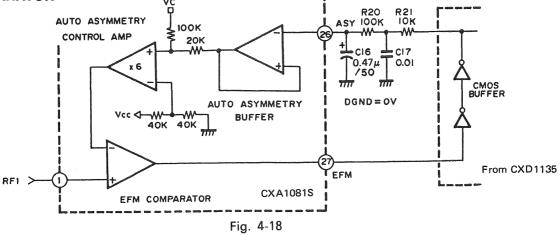

#### **DEFECT CIRCUIT**

After inverting the RFI signal, the Defect circuit performs Bottom Hold using two time constants, one long and one short. The Bottom Hold performed by the short time constant sends a response at a mirror-surface defect on the disc that is 0.1 ms or longer. The Bottom Hold performed using the long time constant continues holding the mirror surface at the level preceding the defect. The Mirror Defect Detection signal is generated by performing a fine plus level shift of that mirror level by use of C coupling, then making a comparison of both signals.

When this signal is used and the DEFECT output is "H," TRKG error is muted and the playability is improved.

Fig. 4-19

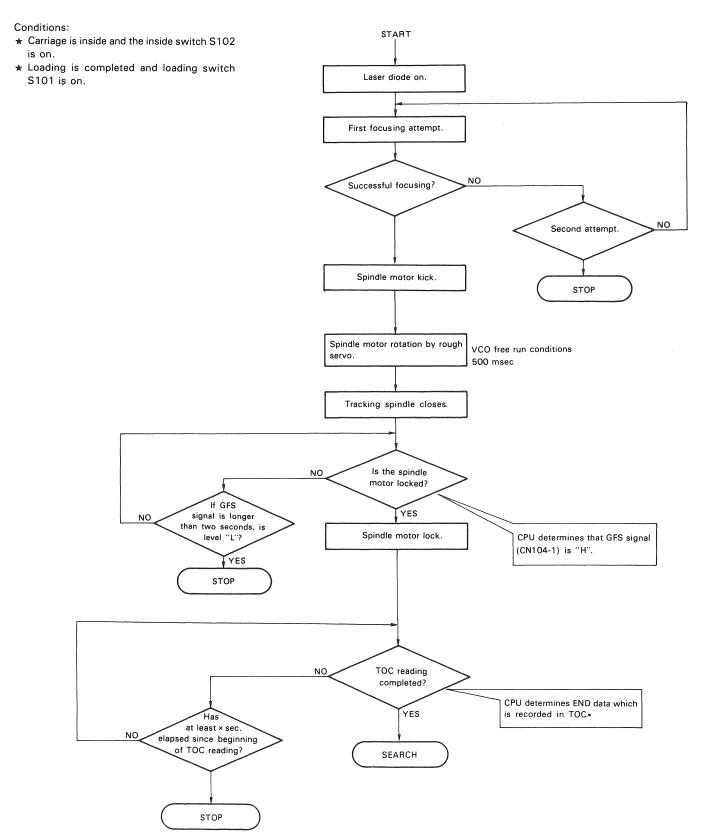

# 4.3 TOC READING

# Initial Settings for Reading of Table of Contents

# 4.4 CARRIAGE SERVO SYSTEM

The carriage servo system inputs the TRKG actuator's drive voltage, and through the carriage servo EQ shown in Fig. 4-20, the amount required for the carriage movement is obtained.

Also, the carriage's LOCATE operation obtains LOCATE voltage by switching over the internal current source in the serial data. This voltage is about 6V. However, during startup and lock, since the output current is limited to 200mA, the voltage will become lower than 6V.

Fig. 4-20

Fig. 4-21

# 4.5 DEMODULATOR

The demodulator is composed primarily of LSI CXD1135Q; it also includes a small amount of added-on circuits. Its functions are:

- 1. Bit clock regeneration using the EFM-PLL circuit.

- 2. Demodulation of the EFM data.

- 3. Detection, protection and internal extension of the frame sync signal.

- 4. Thorough error detection and correction.

- 5. Interpolation using averaging or previous value hold.

- 6. Demodulation of the sub-code and error detection for sub-code Q.

- 7. CLV servo for the spindle motor.

- 8. 8-bit tracking counter.

- 9. CPU interface using the serial bus.

- 10. Built-in 35th digital filter.

Fig. 4-22

Fig. 4-23

# 4.6 DIGITAL LEVEL CONTROL (Only for PD-7050 and PD-7050-S)

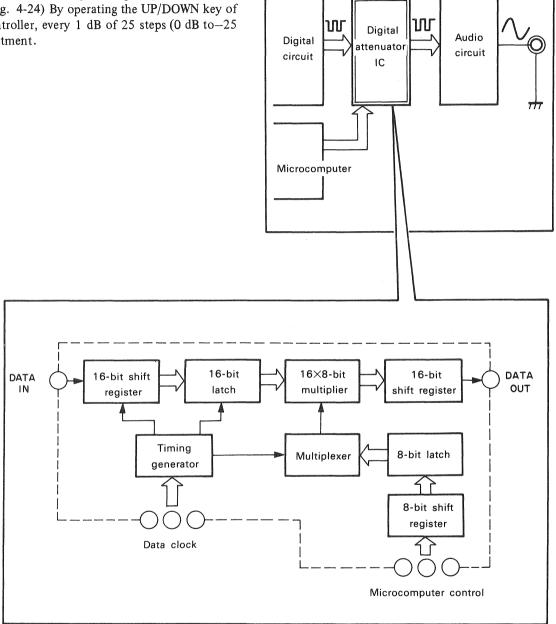

Instead of the previous method, place a digital attenuator IC in front of the audio circuit. By controlling the output level with an 8-bit data of the microcomputer and a 16-bit audio signal from the digital circuit and multiplying both within the attenuator IC, it is possible to obtain an audio signal which does not damage the quality of the audio circuit. (See Fig. 4-24) By operating the UP/DOWN key of the remote controller, every 1 dB of 25 steps (0 dB to-25 dB) level adjustment.

Digital level control

Fig. 4-24 Digital level control